Hypex Electronics BV Kattegat 8 9723 JP Groningen, The Netherlands +31 50 526 4993 sales@hypex.nl www.hypex.nl

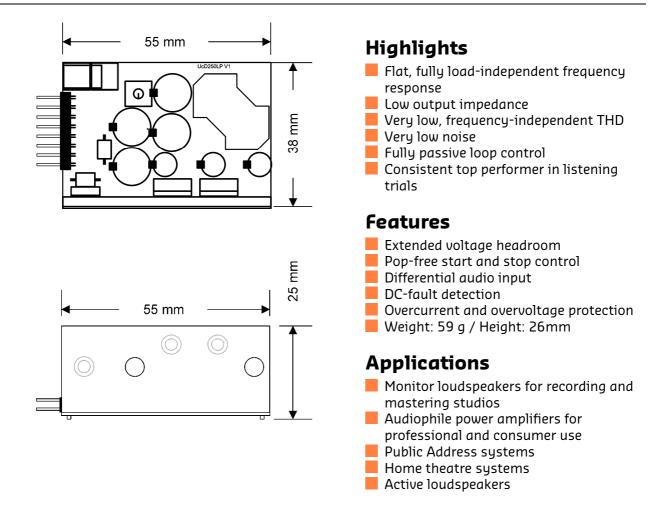

### High Efficiency Power Amplifier Module (Low Profile OEM Version)

# Description

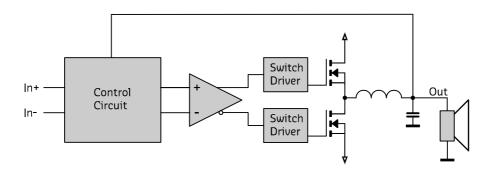

The UcD400LP (Low Profile Low Profile OEM version) amplifier module is a self-contained highperformance class D amplifier intended for a wide range of audio applications, ranging from Public Address systems to ultrahigh-fidelity replay systems for studio and home use. Chief distinguishing features are flat frequency response irrespective of load impedance, nearly frequency-independent distortion behaviour and very low radiated and conducted EMI. Control is based on a phase-shift controlled self-oscillating loop taking feedback only at the speaker output.

# Contents

| Con | tents                            | . 2 |

|-----|----------------------------------|-----|

|     | Performance data                 |     |

|     | Audio Input Characteristics      |     |

|     | Absolute maximum ratings         |     |

|     | Recommended Operating Conditions |     |

|     | Connections                      |     |

|     | Input buffer recommendation      |     |

|     | Typical Performance Graphs       |     |

|     | Connector layout                 |     |

# 1 Performance data

Power supply = +/-64V, Load=4 $\Omega$ , MBW=40kHz, Source imp=40 $\Omega$  ,unless otherwise noted

| ltem                     | Symbol | Min  | Тур    | Max  | Unit | Notes                                                     |

|--------------------------|--------|------|--------|------|------|-----------------------------------------------------------|

| Output Power             | PR     | -    | 400    | -    | W    | THD=1%, Load=4Ω                                           |

|                          |        | -    | 250    | -    | W    | THD=1%, Load=8Ω                                           |

| Distortion               | THD+N  | -    | 0.02   | 0.05 | %    | 20Hz <f<20khz<sup>1) Pout<p<sub>R/2</p<sub></f<20khz<sup> |

|                          |        | -    | 0.003  | 0.02 | %    | 20Hz <f<20khz pout="1W&lt;/td"></f<20khz>                 |

| Output noise             | UN     | -    | 20     | 25   | μV   | Unwtd, 20Hz-20kHz                                         |

| Output Impedance         | Zout   | -    | -      | 18   | mΩ   | f<1kHz                                                    |

|                          |        | -    | -      | 40   | mΩ   | f<20kHz                                                   |

| Power Bandwidth          | PBW    |      | 20-35k |      | Hz   | 2)                                                        |

| Frequency Response       |        | 10   | -      | 50k  | Hz   | +0/-3dB. All loads.                                       |

| Voltage Gain             | Av     | 12.8 | 13     | 13.3 | dB   |                                                           |

| Supply Ripple Rejection  | PSRR   | 52   | 58     | -    | dB   | Either rail, f<1kHz.                                      |

| Required input level for |        |      | 9.00   |      | V    | Appropriate supply voltage                                |

| 400W/4Ω                  |        |      |        |      |      | assumed                                                   |

| Efficiency               | η      |      | 92     |      | %    | Full power                                                |

| ldle Losses              | Po     | -    | 4.3    | 4.6  | W    |                                                           |

| Standby Current          | STBY   | -    | 8      | 10   | mA   | Positive rail                                             |

|                          |        | -    | 12     | 13   |      | Negative rail                                             |

| Current Limit            |        | 16   | 18     | 20   | А    | Hiccup mode after 80ms                                    |

|                          |        |      |        |      |      | limiting                                                  |

**Note 1:** At higher audio frequencies there are not enough harmonics left in the audio band to make a meaningful THD measurement. High frequency distortion is therefore determined using a 18.5kHz+19.5kHz 1:1 two-tone IMD test.

**Note 2:** Dielectric losses in the output capacitor limit long term (>30s) full-power bandwidth to 15kHz.

# 2 Audio Input Characteristics

| ltem               | Symbol          | Min | Тур  | Max | Unit | Notes                  |

|--------------------|-----------------|-----|------|-----|------|------------------------|

| Input Impedance    | Z <sub>IN</sub> |     | 1.8k |     | Ω    | Either input to ground |

| CM Rejection Ratio | CMRR            |     | 58   |     | dB   | All frequencies        |

# 3 Absolute maximum ratings

# Correct operation at these limits is not guaranteed. Operation beyond these limits may result in irreversible damage.

| ltem                  | Symbol          | Rating | Unit | Notes                                                                         |

|-----------------------|-----------------|--------|------|-------------------------------------------------------------------------------|

| Power supply voltage  | VB              | +/-75  | V    | Unit shuts down when either rail exceeds 77V                                  |

| VDR supply voltage    | V <sub>DR</sub> | 20     | V    |                                                                               |

| Peak output current   | OUT,P           | 20     | А    | Unit current-limits at 18A                                                    |

| Input voltage         | VIN             | +/-12  | V    | Either input referenced to ground                                             |

| Air Temperature       | Тамв            | 55     | °C   |                                                                               |

| Heat-sink temperature | Tsink           | 90     | °C   | User to select heat sink to insure this condition under most adverse use case |

# **4** Recommended Operating Conditions

| ltem                   | Symbol          | Min                 | Тур  | Max              | Unit | Notes                           |

|------------------------|-----------------|---------------------|------|------------------|------|---------------------------------|

| Power supply voltage   | VB              | 45 <sup>1)</sup>    | 64   | 73 <sup>2)</sup> | V    |                                 |

| Driver supply voltage  | Vdr             | 14                  | 15.5 | 18               | V    | Referenced to –V <sub>B</sub> . |

| Driver supply current  | I <sub>DR</sub> |                     | 40   |                  | mA   |                                 |

| Load impedance         | ZLOAD           | 1                   |      |                  | Ω    |                                 |

| Source impedance       |                 |                     |      | 100              | Ω    | 50Ω per input                   |

| Effective power supply | CSUP            | 4700μ <sup>3)</sup> |      |                  | F    | Per rail, per attached          |

| storage capacitance    |                 |                     |      |                  |      | amplifier. 4Ω load.             |

| Heat-sink temperature  | Tsink           | 0                   |      | 70               | °C   |                                 |

Note 1: Reduced performance.

Note 2: Unit shuts down when either rail exceeds 77V.

**Note 3:** The effective power supply storage capacitance of Hypex SMPS is already in excess of  $4700\mu$ F. Do not add supplementary capacitance.

# **5** Connections

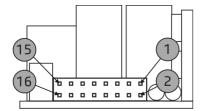

Figure 1: Connector pinning UcD400LP.

### 5.1 J1

In order to ease connecting the amplifier, all necessary connections to operate the amplifier are grouped in one standard 2.54mm pitch dual row 8 pin header.

| Pin  | Туре   | Function                                         |  |

|------|--------|--------------------------------------------------|--|

| 1, 3 | Input  | Negative power supply connection                 |  |

| 2, 4 | Input  | Positive power supply connection                 |  |

| 5    | Output | Amplifier ready                                  |  |

| 6    | Input  | Power supply ground connection <sup>1)</sup>     |  |

| 7    | Input  | ON/OFF control (Active low)                      |  |

| 8    | Output | DC-fault detection (Open collector - Active low) |  |

| 9    | Input  | Non-inverting audio input                        |  |

| 10     | Input  | Inverting audio input                       |

|--------|--------|---------------------------------------------|

| 11, 13 | Output | Loudspeaker connection (hot)                |

| 12, 14 | Output | Loudspeaker connection (cold) <sup>1)</sup> |

| 15     | Output | Current limiter monitoring.                 |

| 16     | Input  | Driver voltage                              |

Note 1: Pin 6,12 and 14 are physically connected to the same potential (ground).

### 5.2 Heatsink connection

The heatsink of the UcD400LP is connected to ground with 2x100nF capacitors.

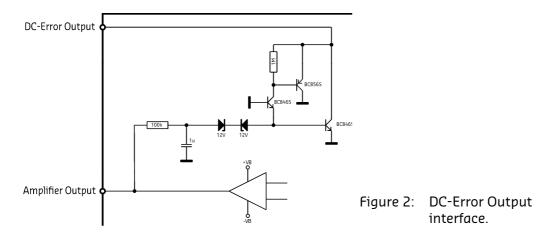

### 5.3 DC-Error Detection Characteristics

The UcD400LP has an integrated DC-error detection which will pull pin 8 low in case of such an event. It is recommended to sense this fault condition and to interrupt both power supply lines in such an event.

| ltem                       | Туре   | Min | Тур | Max | Unit | Notes                                 |

|----------------------------|--------|-----|-----|-----|------|---------------------------------------|

| Voltage on pin 8, DC-error | Output |     |     | 1   | V    | Internal open collector <sup>1)</sup> |

**Note 1:** Must be pulled to a positive voltage by means of an external resistor. Open collector maximum output current: 100mA. Maximum collector voltage: 65V.

#### 5.4 Amplifier On/OFF Characteristics

Pulling pin 7 low enables the amplifier. Leaving pin 7 floating will put the amplifier in standby. This pin may be driven from a logical output or an open collector.

| ltem                            | Min | Тур | Max | Unit | Notes                |  |

|---------------------------------|-----|-----|-----|------|----------------------|--|

| Voltage on pin 7, left floating |     |     | 3   | V    | Internally pulled up |  |

| Pull-up current                 | 20  |     | 60  | uA   |                      |  |

| Threshold voltage               | 1.8 | 2.2 | 2.7 | V    |                      |  |

| Permissible voltage range       | -5  | -   | 75  | V    |                      |  |

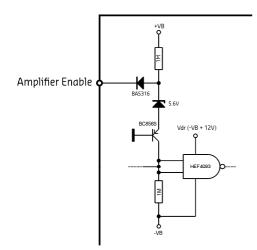

Figure 3:. Amplifier On/Off Control interface.

#### 5.5 Amplifier Ready Characteristics

Pin 5 is pulled low when the amplifier is operating normally and becomes high when the amplifier is muted or shut down due to an error such as overvoltage or overcurrent. Source and sink currents are kept low to allow clamping by the internal diodes of an attached logic input. Pin 5 may be held at or forced to any voltage between -0.6 and 5.2V without error.

| ltem                              | Min  | Тур  | Max | Unit | Notes |

|-----------------------------------|------|------|-----|------|-------|

| Open-circuit voltage (ready=low)  | -0.6 | -0.4 | 0   | V    |       |

| Open-circuit voltage (muted=high) | 4    | 5    | 5.6 |      |       |

| Source current (high)             | 20   | -    | 60  | uA   |       |

| Sink current (low)                | 40   | -    | 80  | uA   |       |

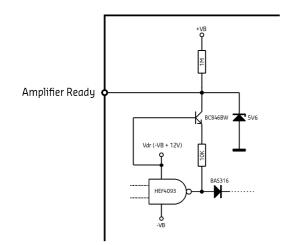

Figure 4: Amplifier Ready interface.

#### 5.6 Current Limiter Monitoring

The current limiter monitor output is pulled low each time a switching period is cut short by current limiting. This output is not latched/delayed and produces very short pulses.

| Item                            | Min  | Тур  | Max | Unit | Notes |

|---------------------------------|------|------|-----|------|-------|

| Open-circuit voltage (limiting) | -0.6 | -0.4 | 0   | V    |       |

| Open-circuit voltage (normal)   | 4    | 5    | 5.6 |      |       |

| Source current (high)           | 20   | -    | 60  | uA   |       |

| Sink current (low)              | 140  | -    | 180 | uA   |       |

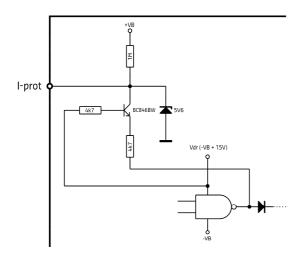

Figure 5: Current limiter monitoring.

### 5.7 Amplifier start-up delay

During initial power up the amplifier is disabled for approx. 1.5s regardless of the state of pin 7. Once powered up there is no start or stop delay. Pin 5 (Amplifier Ready) remains high during the initial power up.

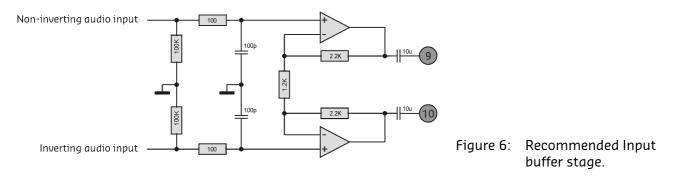

# 6 Input buffer recommendation

The UcD400LP (Low Profile OEM version) has no on-board input buffer. Applications that require a higher gain and/or a higher input impedance benefit from a buffer stage like shown below.

# 7 Typical Performance Graphs

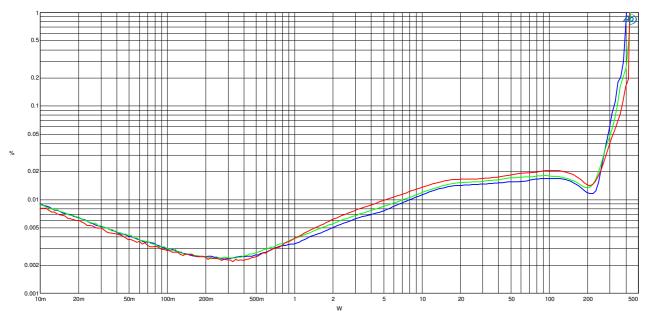

### 7.1 THD vs. Power ( $4\Omega$ )

100Hz (blue), 1kHz (green), 6kHz (red)

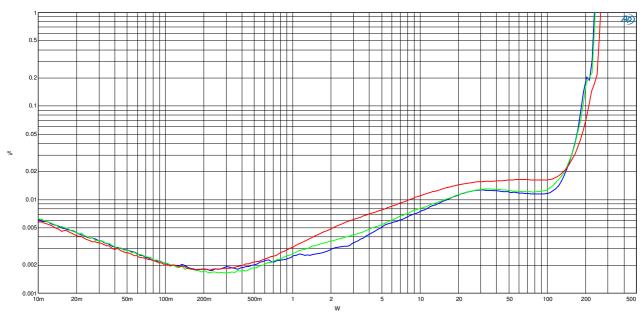

### 7.2 **THD vs Power (8**Ω)

100Hz (blue), 1kHz (green), 6kHz (red)

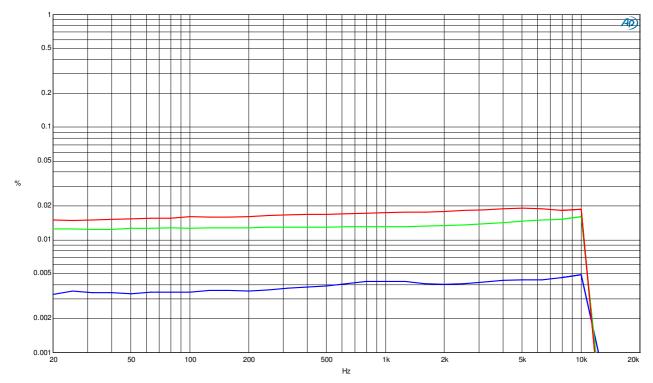

### 7.3 **THD vs. Frequency (4** $\Omega$ )

1W (blue), 10W (green), 50W (red)

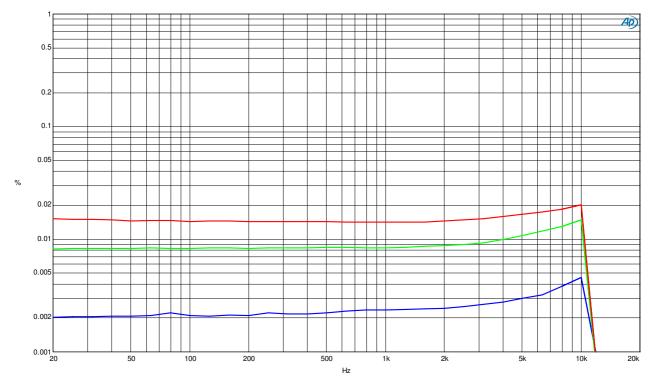

### 7.4 **THD vs. Frequency (8** $\Omega$ )

<sup>1</sup>W (blue), 10W (green), 50W (red)

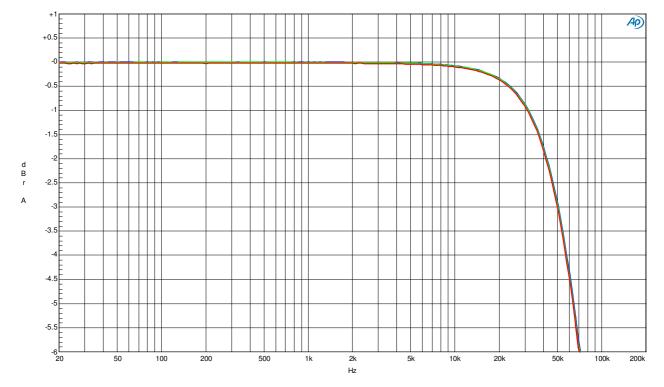

# **7.5** FrequencyResponse ( $4\Omega$ , $8\Omega$ and open circuit)

Open circuit (blue),  $8\Omega$  (green),  $4\Omega$  (red)

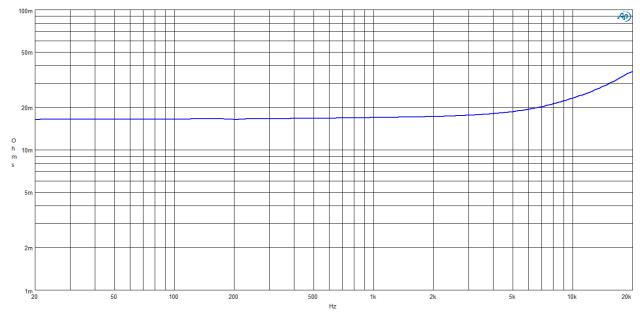

## 7.6 Output Impedance

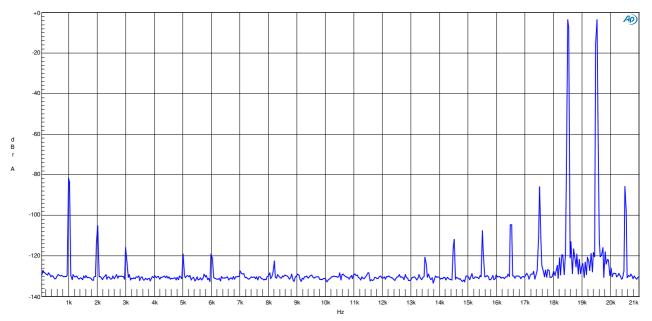

## **7.7** IMD Spectrum18,5kHz + 19,5kHz (8Ω, 10W)

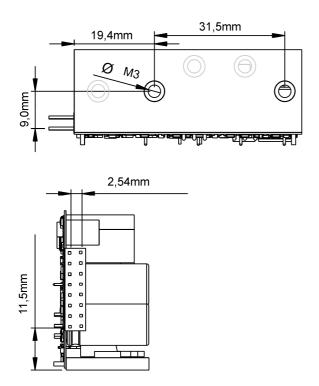

# 8 Connector layout

### 8.1 Front view and Side view

DISCLAIMER: This subassembly is designed for use in music reproduction equipment only. No representations are made as to fitness for other uses. Except where noted otherwise any specifications given pertain to this subassembly only. Responsibility for verifying the performance, safety, reliability and compliance with legal standards of end products using this subassembly falls to the manufacturer of said end product.

LIFE SUPPORT POLICY: Use of Hypex products in life support equipment or equipment whose failure can reasonably be expected to result in injury or death is not permitted except by explicit written consent from Hypex Electronics BV.

| Document<br>Revision | PCB<br>Version | Description                      | Date       |

|----------------------|----------------|----------------------------------|------------|

| R1                   | UcD400LPOEM V1 | Initial Draft.                   | 22.08.2014 |

| R2                   | UcD400LPOEM V1 | External VDR information updated | 29.07.2020 |