Hypex Electronics BV Kattegat 8 9723 JP Groningen, The Netherlands +31 50 526 4993 sales@hypex.nl www.hypex.nl

### Ultrahigh performance class D amplifier

# Highlights

- Extremely low distortion over frequency and power range

- Extremely low output impedance

- Extremely low noise

- Extremely neutral and transparent

#### **Features**

- Differential audio input

- Up to +/-98V operation

- 38A current capability

- Extensive, microprocessor-controlled error protection

### **Applications**

- Audiophile stand-alone power amplifiers for professional and consumer use

- Active loudspeakers for recording and mastering studios

- Very high-end home theatre systems

## Description

The NC1200 amplifier module is an extremely high-quality audio power amplifier module which operates in class D. Not only does it offer a way for audiophile music reproduction to continue in an ever more energy-conscious world, its measured and sonic performance actually raises the bar for audio amplifiers of any description. Operation is based on a non-hysteresis  $5^{th}$  order self-oscillating control loop taking feedback only at the speaker output.

### **Contents**

| 1 | Performance data                 | 3 |

|---|----------------------------------|---|

| 2 | Audio Input Characteristics      | 3 |

|   | Control I/O Characteristics      |   |

|   | Absolute maximum ratings         |   |

|   | Recommended Operating Conditions |   |

|   | Connections                      |   |

|   | Microprocessor functions         |   |

|   | Options                          |   |

|   | Typical performance graphs       |   |

|   | Mechanical drawina               |   |

### 1 Performance data

Power supply = SMPS1200, Load= $4\Omega$ , MBW=20kHz, Source imp= $40\Omega$  ,unless otherwise noted

| Item                     | Symbol            | Min  | Тур    | Max   | Unit | Notes                                     |

|--------------------------|-------------------|------|--------|-------|------|-------------------------------------------|

| Rated Output Power       | PR                | 1200 |        |       | W    | THD=1%, Load=2Ω                           |

|                          |                   | 700  |        |       | W    | THD=1%, Load=4Ω                           |

|                          |                   | 400  |        |       | W    | THD=1%, Load=8Ω                           |

| Distortion               | THD+N,            |      |        | 0.004 | %    | 20Hz <f<20khz<sup>1), 4Ω</f<20khz<sup>    |

|                          | IMD <sup>1)</sup> |      |        |       |      | Pout <pr 2<="" td=""></pr>                |

|                          |                   |      |        | 0.001 | %    | 20Hz <f<20khz pout="1W&lt;/td"></f<20khz> |

| Output noise             | Un                |      | 7      | 8     | μV   | Unwtd, unbuffered                         |

|                          |                   |      | 20     | 28    |      | Unwtd, standard buffer                    |

| Signal-to-noise ratio    | SNR               |      | 137    |       | dB   | P <sub>R</sub> , unbuffered               |

| (unweighted, add 2dB for |                   |      | 128    |       |      | P <sub>R</sub> , buffered                 |

| A-weighted)              |                   |      | 112    |       |      | 1W 8Ω, unbuffered                         |

|                          |                   |      | 103    |       |      | 1W 8Ω, buffered                           |

| Output Impedance         | Zout              |      |        | 2     | mΩ   | f<1kHz                                    |

|                          |                   |      |        | 3     | mΩ   | f<20kHz                                   |

| Power Bandwidth          | PBW               |      | 20-35k |       | Hz   | 2)                                        |

| Frequency Response       |                   | 0    |        | 50    | kHz  | +0/-3dB. All loads.                       |

| Voltage Gain             | A۷                | 27.6 | 27.8   | 28    | dB   | Buffered                                  |

|                          |                   | 11.4 | 11.6   | 11.8  |      | Unbuffered                                |

| Supply Ripple Rejection  | PSRR              | 75   | 80     |       | dB   | Either rail, f<1kHz.                      |

| Efficiency               | η                 |      | 93     |       | %    | Full power                                |

| Idle Losses              | P <sub>0</sub>    |      | 15     | 17    | W    |                                           |

| Current Limit            |                   | 34   | 38     | 40    | А    | Hiccup mode after 200ms limiting          |

**Note 1:** At higher audio frequencies there are not enough harmonics left in the audio band to make a meaningful THD measurement. High frequency distortion is therefore determined using an 18.5kHz+19.5kHz 1:1 two-tone IMD test.

# **2 Audio Input Characteristics**

| Item               | Symbol             | Min | Тур  | Max | Unit | Notes           |

|--------------------|--------------------|-----|------|-----|------|-----------------|

| DM Input Impedance | Z <sub>IN,DM</sub> |     | 5.3k |     | Ω    | Unbuffered      |

|                    |                    |     | 94k  |     |      | Standard buffer |

| CM Input Impedance | ZIN,CM             |     | 6.3k |     | Ω    | Unbuffered      |

|                    |                    |     | 2.2M |     |      | Standard buffer |

| CM Rejection Ratio | CMRR               |     | 55   |     | dB   | All frequencies |

# 3 Control I/O Characteristics

| Item                       | Symbol | Min  | Тур | Max | Unit | Notes                      |

|----------------------------|--------|------|-----|-----|------|----------------------------|

| Weak Pullup                | Rwpu   |      | 27k |     | Ω    | To 3.3V                    |

| Logical high input voltage | ViH    | 2.65 |     | 3.6 | V    | nAMPON, SCL, SDA           |

| Logical low input voltage  | VIL    | -0.3 |     | 0.5 | V    | nAMPON, SCL, SDA           |

| Logical high leakage       | Іон    |      |     | 1μ  | Α    | SCCP, CLIP, FATAL          |

| current                    |        |      |     |     |      |                            |

| Logical low output voltage | Vol    |      |     | 0.4 | V    | SCCP, CLIP, FATAL, IoL=1mA |

# 4 Absolute maximum ratings

Correct operation at these limits is not guaranteed. Operation beyond these limits may

result in irreversible damage.

| result in irreversible dumage. |          |        |      |                                                           |  |  |  |  |

|--------------------------------|----------|--------|------|-----------------------------------------------------------|--|--|--|--|

| Item                           | Symbol   | Rating | Unit | Notes                                                     |  |  |  |  |

| Power supply voltage           | VB       | +/-105 | V    | See section 7.2                                           |  |  |  |  |

| VDR supply voltage             | $V_{DR}$ | 20     | V    | Floating and referenced to V <sub>B</sub> See section 7.2 |  |  |  |  |

| Signal stage supply            | Vsig     | +/-15  | V    | No local regulators                                       |  |  |  |  |

| voltage                        |          | +/-25  |      | Local regulators installed                                |  |  |  |  |

| Peak output current            | lout,p   | 40     | Α    | Unit current-limits safely at 38A                         |  |  |  |  |

| Input voltage                  | Vin      | +/-15  | V    | Buffered only. Either input referenced to                 |  |  |  |  |

|                                |          |        |      | ground                                                    |  |  |  |  |

| Input current                  | lin      | 10m    | Α    | Logical inputs and buffer inputs                          |  |  |  |  |

| Collector voltage              | Voc      | 35     | V    | Open collector outputs when high                          |  |  |  |  |

| Collector current              | loc      | 2m     | Α    | Open collector outputs when low                           |  |  |  |  |

| Air Temperature                | Тамв     | 65     | °C   | Lower improves lifetime                                   |  |  |  |  |

| Heat-sink temperature          | TSINK    | 85     | °C   | Thermistor limited. User to select heat sink to           |  |  |  |  |

| ·                              |          |        |      | insure this condition under most adverse use              |  |  |  |  |

|                                |          |        |      | case                                                      |  |  |  |  |

# **5 Recommended Operating Conditions**

| ltem                                          | Symbol           | Min   | Тур | Max  | Unit | Notes                                               |

|-----------------------------------------------|------------------|-------|-----|------|------|-----------------------------------------------------|

| Power supply voltage                          | Vв               | 35    | 84  | 98   | V    | Available output power depends on supply voltage    |

| Signal stage supply                           | V <sub>SIG</sub> | 12    |     | 15   | V    | No local regulators                                 |

| voltage (positive and negative)               |                  | 16    |     | 25   | V    | Local regulators installed                          |

| Signal stage supply current                   | Ivsig            |       | 40  |      | mA   |                                                     |

| Driver supply voltage                         | VDR              | 14.5  | 15  | 15.5 | V    | Unit protects when allowable range is exceeded      |

| Driver supply current                         | I <sub>DR</sub>  |       | 100 |      | mA   |                                                     |

| Load impedance                                | ZLOAD            | 1     |     |      | Ω    |                                                     |

| Source impedance (unbuffered)                 | Zsrc             |       |     | 100  | Ω    | For correct operation                               |

| Source impedance (buffered)                   |                  |       |     | 1k   |      | For rated noise performance                         |

| Effective power supply storage capacitance 1) | Csup             | 4700μ |     |      | F    | Per rail, per attached amplifier. 4Ω load presumed. |

**Note 1:** The effective power supply storage capacitance of Hypex SMPS is already in excess of 4700uF. Do not add supplementary capacitance.

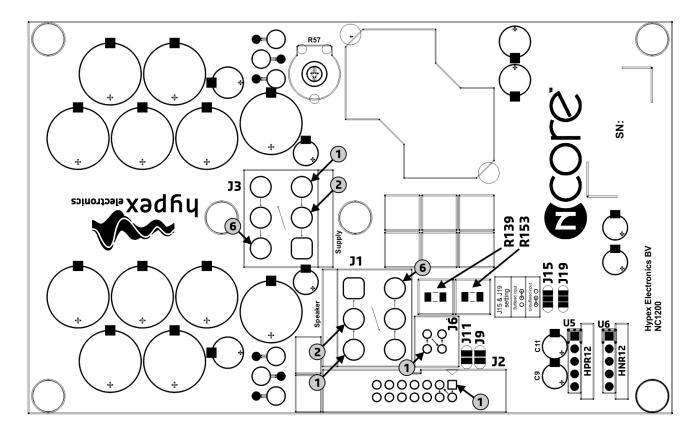

### **6** Connections

### 6.1 J1 Loudspeaker output

Connector type: JST (<u>www.jst.com</u>) B06P-VL. Matching cable part: VLP-06V. Pinout:

| Pin | Туре   | Function                          |

|-----|--------|-----------------------------------|

| 2   | LS out | Loudspeaker output, hot (pair 1)  |

| 3   | LS out | Loudspeaker output, hot (pair 2)  |

| 5   | LS out | Loudspeaker output, cold (pair 1) |

| 6   | LS out | Loudspeaker output, cold (pair 2) |

| 1   | n.c.   | Optional, see section 8           |

| 4   | n.c.   | Optional, see section 8           |

The two pairs of output pins may either be parallelled or used for biwiring. Because of the proximity of the three connectors and the magnitude of the currents, make sure that each pair of wires connected to J1 is twisted. Not twisting can cause crosstalk from the loudspeaker wires back into the audio input, or from the DC power lines (which carry a distorted version of the signal) into the loudspeaker lines.

### 6.2 J2 Control and optional audio input

Connector type: 14-pole, dual row male 2.54mm shrouded (box) header. Mates with female IDC connector. For hardware-controlled modules powered by an SMPS1200, a straight female-to-female ribbon cable is all that is needed.

| Pin              | Туре        | Function                                                                   |

|------------------|-------------|----------------------------------------------------------------------------|

| 1                | Pwr in      | +Vsig, positive supply for op amps: see section 8.                         |

| 2                | Pwr in      | -Vsig, negative supply for op amps: see section 8.                         |

| М                | Pwr         | GND                                                                        |

| 4                | i/o, wpu    | Ready output (HW mode) or SDA (I2C mode). Weakly pulled up                 |

| 5                | o/c         | CLIP: Clip indication. Active low                                          |

| 6                | i/o, wpu    | nAMPON (HW mode)                                                           |

| 7 <sup>3)</sup>  | Analogue in | INH: Audio input, hot                                                      |

| 8 <sup>3)</sup>  | Analogue in | INC: Audio input, cold                                                     |

| 9                | o/c         | SCCP: single-cycle current limiter indication. Active low                  |

| 10               | o/c or i/o  | FATAL (HW mode): Catastrophic fault indication or SCL (I2C mode)           |

| 11 <sup>4)</sup> | i/o         | I <sup>2</sup> C address selection, see section 7.4 Software (I2C) control |

| 12 <sup>4)</sup> | n.c.        |                                                                            |

| 13 <sup>4)</sup> | i/o         | Current monitor output, hot (0.1V per Ampere)                              |

| 14 <sup>4)</sup> | i/o         | Current monitor output, cold                                               |

**Note 1:** o/c=open collector

**Note 2:** wpu=weakly pulled up to 3.3V, not to be driven above 3.3V.

**Note 3:** When using the audio input on J2 (see section 8), refer to section 6.4 for further notes.

**Note 4:** Only available in hardware V4 and up.

### 6.3 J3 Power stage supply

Connector type JST (<u>www.jst.com</u>) B06P-VL. Matching cable part: VLP-06V. Pinout:

| Pin  | Туре   | Function                                                                                                                          |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| 3, 6 | Pwr    | GND: return for +HV and -HV. Parallelled pins for current capacity reasons                                                        |

| 2    | Pwr in | +HV: unregulated supply (nominally +84V)                                                                                          |

| 5    | Pwr in | -HV: unregulated supply (nominally -84V)                                                                                          |

| 1    | Pwr in | VDRH: +15V referenced to pin 4                                                                                                    |

| 4    | Pwr in | VDRL: return for pin 1. A floating 15V supply should be connected between pins 1 and 4. Pin 4 is internally connected with pin 5. |

The SMPS1200 output connects to J3 on a pin-for-pin basis and premade cables can be supplied.

### 6.4 J6 Audio input

Connector type: 2x2 pin Microfit header type 43045-0412 (see <a href="www.molex.com">www.molex.com</a>), Matching cable part 43025-0400.

| Pin | Туре                  | Function                                      |

|-----|-----------------------|-----------------------------------------------|

| 1   | Analogue in           | INH: noninverting audio input                 |

| 2   | Analogue in           | INC: inverting audio input                    |

| 3   | in, wpu <sup>1)</sup> | nAMPON. Electrically connected to pin 6 of J2 |

| 4   | passive               | Ground.                                       |

**Note 1:** wpu=weakly pulled up to 3.3V, not to be driven above 3.3V.

The audio input is DC coupled, this means the audio source has to be free of any DC voltage. The audio input is differential. This means that ground is not part of the audio signal. When connecting an unbalanced source, treat pins 1 and 2 as a floating input with pin 2 being the "audio ground". Pin 4 may be used to attach the shield of a shielded twisted pair cable, but the "audio ground" connection of an unbalanced cable should never connect here.

#### 6.5 J9, J11, J15, J19

Solder jumpers, see section 8 for more information.

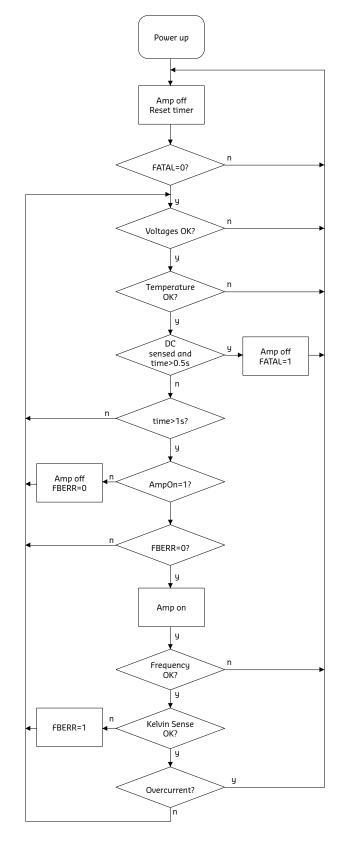

# 7 Microprocessor functions

Whether the module is to be used for hardware or software control is determined by the settings on the address pin, J2-p11.

#### 7.1 Firmware operation

The microprocessor has three main functions: to provide an interface for controlling the amplifier, to monitor the supply voltages in order to prevent spurious operation during power up/down and to detect error conditions. Most errors clear automatically as soon as the error condition lifts. The exception is a fatal DC fault, this almost certainly stems from a broken power FET. The FATAL signal should not be cleared externally. Instead the +/-HV supplies must be shut down immediately to prevent or mitigate damage to attached loudspeakers.

#### 7.2 Protection limits

| Item               | Symbol | Rating | Unit | Notes |

|--------------------|--------|--------|------|-------|

| +/-HV undervoltage |        | 35     | V    |       |

| +/-HV overvoltage  |        | 101    | V    |       |

| VDR undervoltage   |        | 13.5   | V    |       |

| VDR overvoltage    |        | 16     | V    |       |

| Overtemperature    |        | 95     | °C   |       |

| Overtemp, lower    |        | 85     | °C   |       |

| hysteresis         |        |        |      |       |

#### 7.3 Hardware control

When I2C address selection pin (J2 - pin 11) is left unconnected, the amplifier is operated in Hardware mode.

Hardware control consists of a single control line, nAMPON (available both on J2 and J6). Pulling nAMPON low enables the amplifier as soon as all error conditions have been cleared for at least one second. In hardware mode, pin 10 of J2 is the FATAL signal which is pulled low when the power stage suffers an irrecoverable breakdown.

### 7.4 Software (I2C) control

In software mode, pin 10 of J2 is configured as SCL and pin 4 as SDA. These lines should be pulled to 3.3V with 4.7k resistors externally. The I2C bus should be operated at the standard 100kHz rate. Please make sure the I2C bus to this amplifier is isolated from other I2C buses, in order to prevent an I2C bus hangup when the supply for the amplifier is turned off.

#### 7.4.1 Address selection PCB Version 0 - V5

| Voltage level on J2-p11 (Volt) | Addr1         | Addr0         | Resistor value      |

|--------------------------------|---------------|---------------|---------------------|

| 0 to 0,2                       | 0             | 0             | $0\Omega$ to ground |

| 0,6 to 1,0                     | 0             | 1             | 12kΩ to ground      |

| 1,65 (default)                 | Hardware mode | Hardware mode |                     |

| 2,2 to 2,6                     | 1             | 0             | 15kΩ to +3V3        |

| 3,1 to 3,3                     | 1             | 1             | 0Ω to +3V3          |

#### I<sup>2</sup>C slave address

| Bit 0 | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 | Bit 6 | Bit 7 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 1     | 0     | 1     | 1     | 0     | ADDR1 | ADDR0 | R/W   |

#### 7.4.2 Address selection PCB Version V6 and up

The new NC1200 supports up to 16 I2C addresses. Set the address by pulling the I2C address selection pin (J2 -pin 11) to GND through a resistor.

| Pull-down resistor at Pin 11 | Dec I2C address | Binary I2C address |

|------------------------------|-----------------|--------------------|

| 0r                           | 88              | 1011000x           |

| 1.8k                         | 89              | 1011001x           |

| 3.9k                         | 90              | 1011010x           |

| 6.8k                         | 91              | 1011011x           |

| 10k                          | 92              | 1011100x           |

| 12k                          | 93              | 1011101x           |

| 18k                          | 94              | 1011110x           |

| 22k                          | 95              | 1011111x           |

| 27k                          | 96              | 1100000x           |

| 33k  | 97  | 1100001x |

|------|-----|----------|

| 47k  | 98  | 1100010x |

| 56k  | 99  | 1100011x |

| 82k  | 100 | 1100100x |

| 120k | 101 | 1100101x |

| 180k | 102 | 1100110x |

| 390k | 103 | 1100111x |

X=r/w bit.

#### 7.4.3 Register 0: Error monitor bits

| Bit | R/W | Function                                                                              |  |  |  |

|-----|-----|---------------------------------------------------------------------------------------|--|--|--|

| 7   | R   | Amp fail. This bit replaces the FATAL line in I2C mode.                               |  |  |  |

| 6   | R   | Direct short (tested by checking for an abnormally high switching frequency). Cleared |  |  |  |

|     |     | after a mute cycle.                                                                   |  |  |  |

| 5   | R   | Sustained overcurrent condition (hiccup mode). Cleared after a mute cycle.            |  |  |  |

| 4   | R   | -HV undervoltage. Clears as soon as -HV is above the UVP limit.                       |  |  |  |

| 3   | R   | +HV undervoltage. Clears as soon as +HV is above the UVP limit.                       |  |  |  |

| 2   | R   | -HV overvoltage. Clears as soon as -HV has returned below the OVP limit.              |  |  |  |

| 1   | R   | +HV overvoltage. Clears as soon as +HV has returned below the OVP limit.              |  |  |  |

| 0   | R   | DC error. Excessive DC content was found at the output. Cleared after a mute cycle.   |  |  |  |

### 7.4.4 Register 1: Further error monitor bits

| Bit | R/W | Function                                                                     |

|-----|-----|------------------------------------------------------------------------------|

| 7   | R   | Always set to 0                                                              |

| 6   | R   | Always set to 1                                                              |

| 5   |     | Reserved                                                                     |

| 4   |     | Reserved                                                                     |

| 3   | R   | Overtemperature. Clears as soon as temperature has dropped back to the lower |

|     |     | hysteresis limit.                                                            |

| 2   | R   | Amplifier Ready. High when the amplifier is working normally and not muted.  |

| 1   | R   | VDR undervoltage                                                             |

| 0   | R   | VDR overvoltage                                                              |

### 7.4.5 Register 2: Command byte

| Bit | R/W | Function                                  |

|-----|-----|-------------------------------------------|

| 0   | R/W | AmpEnable, write 1 to enable (unmute) amp |

### 7.4.6 Register 3-7: Measured parameters

| Reg | Function                                 |

|-----|------------------------------------------|

| 3   | +HV, in volts                            |

| 4   | -HV, in volts                            |

| 5   | VDR, in tenths of volts                  |

| 6   | NTC reading, contact for further details |

| 7   | Frequency reading in units of 64kHz      |

| 8   | Product number (12 for NC1200)           |

# 8 Options

The standard design offers quite some flexibility already. The following table lists the possible options and notes which are on the stock version

| Option           | Description                                                                                                                                                                                                                                                                | Stock         |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Local regulation | HNR12/HPR12 regulators. Externally supplied voltage should be >15V and <25V, otherwise quality is not important. When this option is not installed, the externally supplied voltage should be regulated and between 12V and 15V, and quality can affect sonic performance. | Installed     |

| Secondary input  | Connects the audio input to pins 7 and 8 of J2. When using J6, it is better not to have two wires in the flat cable header dangling on the end of the audio inputs. This can be selected by solder jumpers J9 and J11. $^{(1)}$                                            | Not connected |

| Input Buffer     | Select buffered, or unbuffered input with solder jumpers J15 and J19. Remove R139 and R153 for unbuffered use <sup>(1</sup>                                                                                                                                                | Buffered      |

| Customization    | Ask sales for MLQ values.                                                                                                                                                                                                                                                  |               |

**Note 1:** Only available in hardware V4 and up.

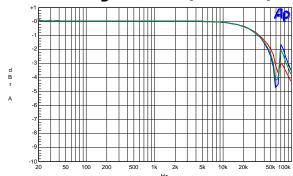

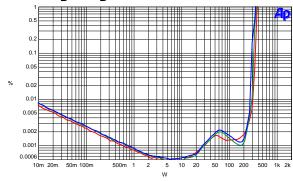

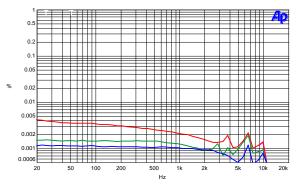

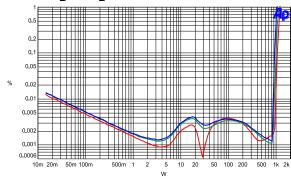

### 9 Typical performance graphs

The graphs were taken on one stock NC1200 module powered by an SMPS1200. Refer to the tables in section 3 for guaranteed limits.

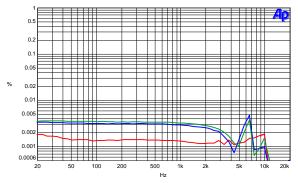

### 9.1 Small signal tests (all loads)

Frequency response into 8 (red), 4 (green) and 2 (blue) ohms

Output impedance, measured directly at J1

### 9.2 Large signal tests ( $8\Omega$ )

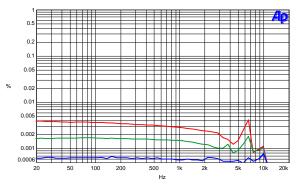

THD vs power at 100Hz (blue), 1kHz (green) and 6kHz (red)

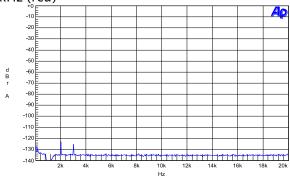

Distortion residual at 1W, 1kHz.

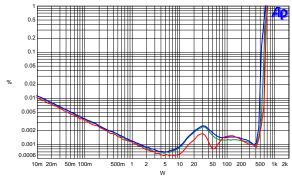

THD vs frequency at 10W (blue), 100W (green) and 250W (red)

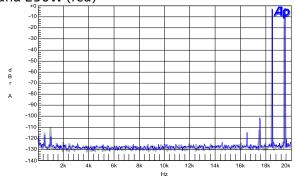

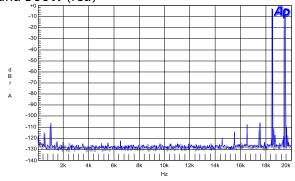

IMD spectrum at 18.5kHz+19.5kHz, 50W+50W. Peak voltage corresponds to a 200W sine. Grey background = test instrument.

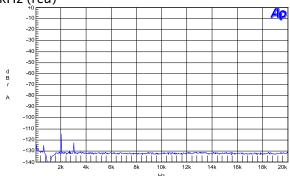

## 9.3 Large signal tests ( $4\Omega$ )

THD vs power at 100Hz (blue), 1kHz (green) and 6kHz (red)  $^{\circ}$

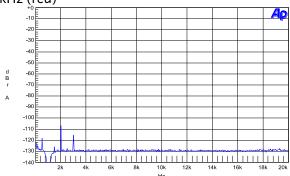

Distortion residual at 1W, 1kHz.

THD vs frequency at 10W (blue), 100W (green) and 500W (red)

IMD spectrum at 18.5kHz+19.5kHz, 100W+100W. Peak voltage corresponds to a 400W sine. Grey background = test instrument.

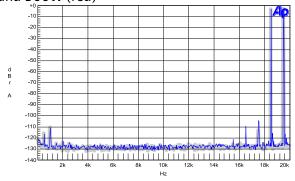

### 9.4 Large signal tests $(2\Omega)$

THD vs power at 100Hz (blue), 1kHz (green) and 6kHz (red)

Distortion residual at 1W, 1kHz.

THD vs frequency at 10W (blue), 100W (green) and 500W (red)

IMD spectrum at 18.5kHz+19.5kHz, 100W+100W. Peak voltage corresponds to a 400W sine. Grey background = test instrument.

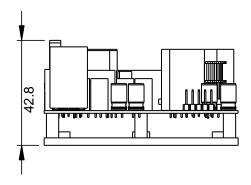

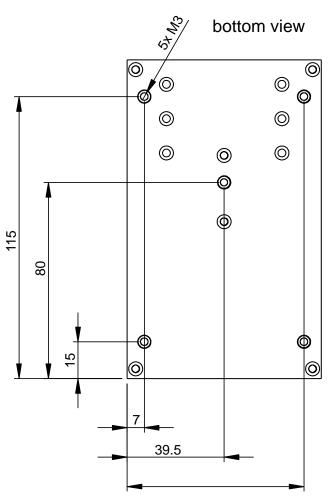

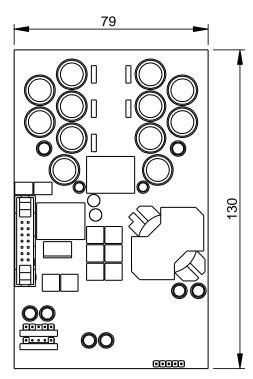

## 10 Mechanical drawing

**Note:** Not shown is the mated JST VL connector. The mated height is 29.2mm, for a total module height of 43.8mm. Add bend radius and wire thickness to obtain final minimum required height for the mounted assembly.

DISCLAIMER: This subassembly is designed for use in music reproduction equipment only. No representations are made as to fitness for other uses. Except where noted otherwise any specifications given pertain to this subassembly only. Responsibility for verifying the performance, safety, reliability and compliance with legal standards of end products using this subassembly falls to the manufacturer of said end product.

LIFE SUPPORT POLICY: Use of Hypex products in life support equipment or equipment whose failure can reasonably be expected to result in injury or death is not permitted except by explicit written consent from Hypex Electronics BV.

| Document | PCB              | Description                                                  | Date       |

|----------|------------------|--------------------------------------------------------------|------------|

| Revision | Version          |                                                              |            |

| R0       | NC1200 V1        | Draft/Preliminary                                            | 13.09.2011 |

| R1       | NC1200 V1        | Expanded noise spec                                          |            |

|          |                  | JST VL pinout numbering per JST spec                         |            |

|          |                  | Clarified storage capacitance                                |            |

|          |                  | Correction to descriptions of registers 1 and 2.             |            |

| R2       | NC1200 V3        | Note added for DC coupled audio input.                       |            |

|          |                  | Format changed                                               | 07.12.2012 |

|          |                  | Connections drawing added                                    |            |

| R3       | NC1200 V4 and up | I2C functionality added                                      | 21.05.2013 |

|          |                  | Updated for V5 PCB                                           |            |

| R5       | NC1200 V4 and up | J1 pin out description updated                               | 03.01.2014 |

|          |                  | I <sup>2</sup> C address selection updated for PCB V6 and up |            |

| R6       | NC1200 V4 and up | I <sup>2</sup> C hang-up prevent information added           |            |

| R7       | NC1200 V4 and up | Removed irrelevant information                               | 08.02.2019 |

| R8       | NC1200 V4 and up | Added absolute maximum rating Vsig                           | 18.02.2019 |

| R9       | NC1200 V4 and up | Correction in table I <sup>2</sup> C addresses               | 14.06.2019 |

| R10      | NC1200 V4 and up | Instruction added for unbuffered use                         | 08.08.2019 |